# Record Power Added Efficiency, Low Voltage GOI (GaAs On Insulator) MESFET Technology for Wireless Applications

*Primit Parikh, James Ibbetson, Umesh Mishra*

*ECE Department, University of California, Santa Barbara, CA. 93106*

*Daniel Docter, Minh Le, Kursad Kiziloglu, David Grider*

*Hughes Research Laboratories, Malibu, CA 90265*

*Joe Pusl*

*Hughes Space and Communications, Los Angeles, CA.*

*This work supported by AFOSR (PRET) and DARPA (OTC) research contracts*

## ABSTRACT

A record high power added efficiency is obtained from a GaAs On Insulator (GOI) MESFET.  $\text{Al}_2\text{O}_3$  obtained by the wet oxidation of  $\text{Al}_{0.98}\text{GaAs}$  in steam, is used as the insulating buffer layer. The insulating buffer results in elimination of buffer leakage and enhanced charge control. 0.35  $\mu\text{m}$  gate length GOI MESFETs exhibit a PAE of **72 %** at a drain voltage of **3 Volts at 4 GHz**.

## INTRODUCTION

High performance power amplifiers with high power added efficiency (PAE) are a crucial requirement for modern wireless communication applications. While GaAs and InP based HEMTs [1] and HBTs [2] are viable candidates for these needs, GaAs MESFETs are very attractive due to their relative simplicity and lower cost [3]. We have developed GaAs On Insulator (**GOI**) devices for a high efficiency and linearity technology [4].  $\text{Al}_2\text{O}_3$  obtained by the wet oxidation of  $\text{Al}_x\text{Ga}_{1-x}\text{As}$  in steam [5] is used as the insulating buffer layer, which results

in the elimination of substrate leakage current leading to higher output resistance and improvement in the pinchoff characteristics. This gets translated to high efficiency operation as a power amplifier. At 4 GHz, PAE of 67.7 % at a low drain bias of 3 Volts, with output power 75 mW/mm was obtained. With harmonic tuning [6], a PAE of 72 % was achieved. To the best of our knowledge, this is the **highest** reported PAE for a GaAs MESFET under these conditions.

## FABRICATION

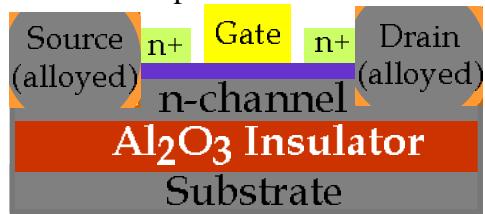

The epilayer structure and device schematic of the GOI MESFET is shown in fig 1 and 3 respectively.

|                                                                              |

|------------------------------------------------------------------------------|

| 200 Å GaAs, cap                                                              |

| 30 Å AlAs                                                                    |

| 50 Å InAs, $n=10^{19}$                                                       |

| $10 \times (5 \text{ Å InAs, } n^{++} / 10 \text{ Å GaAs } n^{++})$          |

| 50 Å $\text{Al}_{0.7}\text{GaAs}$ , $n=1 \times 10^{17}/\text{cm}^3$         |

| 100 Å $\text{Al}_{0.3}\text{GaAs}$ barrier, $n=1 \times 10^{17}/\text{cm}^2$ |

| 1000 Å GaAs channel $n=4 \times 10^{17}$                                     |

| 50 Å $\text{Al}_{0.30}\text{GaAs}$ spacer, undoped                           |

| 100 Å grade, $\text{Al}_{0.98}\text{GaAs}$ to $\text{Al}_{0.30}\text{GaAs}$  |

| 500 Å $\text{Al}_{0.98}\text{GaAs}$ oxidation layer                          |

| 3000 Å LT-AlGaAs                                                             |

| S. I. GaAs Substrate                                                         |

Fig 1. Epitaxial layer structure of the GOI MESFET

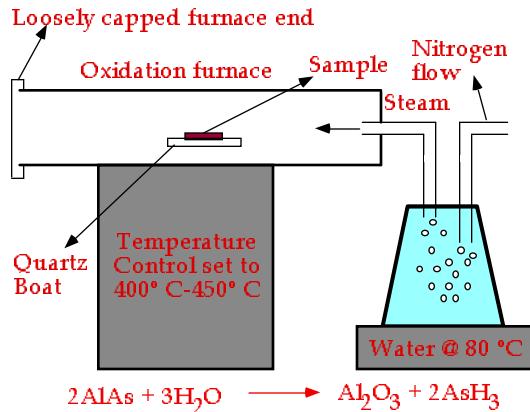

The LT-AlGaAs layer below the buffer layer insulator, serves as a getterer for Arsenic released during oxidation and helps in minimizing any charge depletion resulting from oxidation [5]. The undoped GaAs cap layer protects the active device from any unwanted oxidation from the top. The fabrication starts with mesa isolation by  $\text{BCl}_3/\text{Cl}_2/\text{SiCl}_4$  based reactive ion etching, simultaneously exposing the  $\text{Al}_{0.98}\text{GaAs}$  buffer layer from the side. Next is the lateral wet oxidation of the  $\text{Al}_{0.98}\text{GaAs}$ . The oxidation is done in steam which is introduced into a quartz furnace maintained at the desired oxidation temperature ( $420^\circ \text{C}$ ) by means of nitrogen carrier gas bubbling through water at  $85^\circ \text{C}$  (fig 2).

Fig 2. Oxidation Furnace Schematic

After this, the GaAs cap and the thin AlAs etch stop layers are removed using selective citric acid based etching and phosphoric acid based etching respectively. Then, Ni/Ge/Au/Ni/Au contacts are evaporated and alloyed to form the source and drain regions. Next the  $0.35 \mu\text{m}$  T-Gates are written by E-beam lithography. Recess etching is done by selective citric acid based etchant. Ti/Pt/Au Schottky metallization completes the device. Control MESFETs are also fabricated in the same fashion, except that the oxidation step is omitted.

Fig 3. GOI MESFET schematic

## RESULTS and DISCUSSION

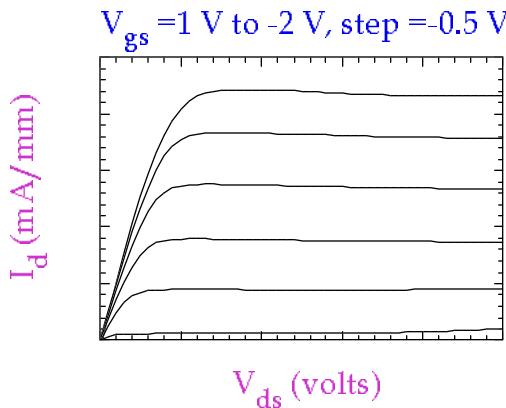

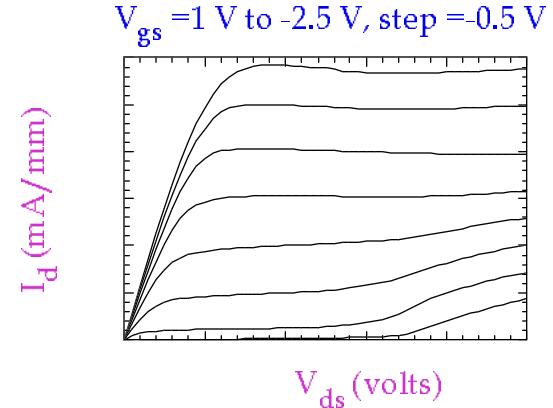

The DC I-V characteristics of the GOI (oxidized buffer) and the control MESFET are shown in fig 4a and 4b.

Fig 4 a. I-V characteristics of the  $0.35 \mu\text{m} \times 100 \mu\text{m}$  GOI MESFET

As evident, the oxidized buffer results in a lower output conductance, and also better pinchoff characteristics due to the elimination of substrate leakage. The  $I_{dss}$  (channel current at  $V_{gs}=0$ ) of the GOI MESFET is 270 mA/mm and that of the control MESFET is 400 mA/mm. The peak  $g_m$  of the devices is around 190 mS/mm. The two terminal diode breakdown voltage is 11V (@ 1 mA/mm current). The slight current reduction comes about due to backdepletion at the oxide-channel interface. However this has been minimized to about 130 mA / mm which

Fig 4b. I-V characteristics of the  $0.35 \mu\text{m} \times 100 \mu\text{m}$  GOI MESFET corresponds to charge density in the  $10^{11}/\text{cm}^2$  range, much lower than the previous observed values of over 300 mA/mm [4]; due to the As gettering effect of the LT AlGaAs buffer. S-parameter measurements were done on HP 8510B network analyzer.

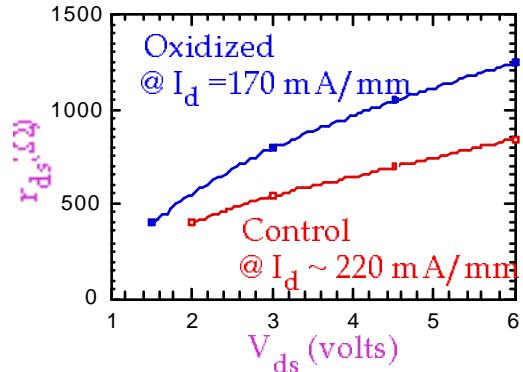

Fig 5. Extracted RF output resistance of the oxidized (GOI) and control device (width=100μm)

The short circuit current gain cutoff frequency  $f_t$  and the maximum oscillation frequency  $f_{max}$  were determined to be 23 GHz and 75 GHz respectively for the GOI device, at  $V_{ds}=3\text{V}$  and  $I_d= 170 \text{ mA/mm}$ .

These were 23 GHz and 70 GHz for the

unoxidized device. The  $f_t$ 's are similar as expected, indicating that electron velocity is unaffected by the oxidation process. The  $f_{max}$  of the oxidized device is higher due to an improvement in  $r_{ds}$ . The extracted RF output resistance (from s-parameter data) for the oxidized and control device is shown in fig 5.

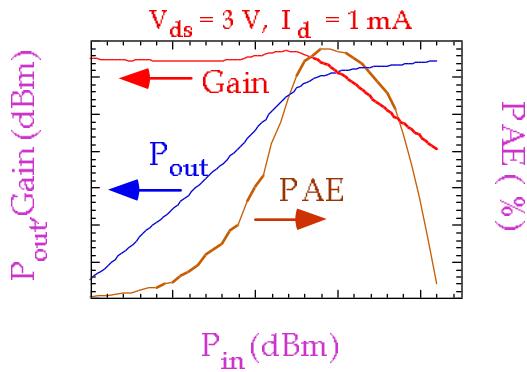

Power and efficiency measurements were performed at 4 GHz using the ATN LP1 load pull system. The GOI device had an efficiency of 67.7 % at a low drain bias of 3V with an associated output power of 75 mW/mm; under class B biasing conditions [fig 6]. The highest efficiency obtainable from the control device was 58 % under similar conditions. This is illustrative of the benefit of the insulating buffer in having superior charge control and sharper pinchoff characteristics.

Fig 6. Power and efficiency measurements for 0.35  $\mu$ m x 150  $\mu$ m GOI MESFET. The GOI device performed very well even with an ultra low drain bias of 1.5 V, with a

PAE of 57 % and  $P_{out}$  of 30 mW/mm. Class A operation ( $V_{ds} = 5V$ ,  $I_{ds} = 200$  mA/mm) resulted in a  $P_{out}$  of 410 mW/mm with a PAE of 48 %. All the measurements were optimized for maximum efficiency.

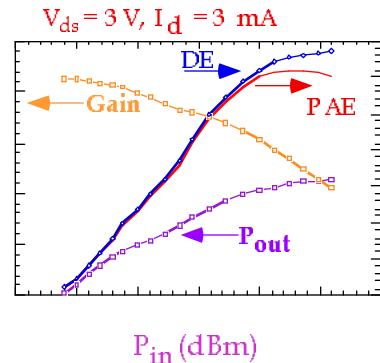

Active Load Pull measurements [6,7] with 2'nd and 3'rd harmonic matching, resulted in a PAE of 72 % [fig 7] at an output power level of 85 mW/mm at 4 GHz with  $V_{ds}$  of 3 V. These results represent the highest reported PAE for a GaAs based MESFET operating under the above conditions.

Fig 7. Power and efficiency measurements for 0.35  $\mu$ m x 150  $\mu$ m GOI MESFET with Active load pull and harmonic matching.

## CONCLUSION

We have demonstrated GOI (GaAs On Insulator) MESFET technology for high efficiency wireless communications. The GOI devices with an Aluminum Oxide insulating buffer exhibited PAE of 72 % at 4 GHz and a low  $V_{ds}$  of 3 V, at an output power of 85 mW/mm, a **record** for GaAs based MESFETs under these conditions. 1.5

volt operation was also demonstrated with a PAE of 57 %. This performance is achieved by the insulating buffer which results in elimination of substrate leakage, better pinchoff characteristics and improved charge control.

## REFERENCES

1. H. Uno, Y. Ummoyo, M. Mori, M. Miyazaki A. Terano, M. Kudo, "Pseudomorphic Power HEMT with 53.5 % Power added efficiency for 1.5 GHz PHS standards", IEEE MTT-S Dig., 1996 pp.547-550.

2. C. Kim, N. Hayama, H. Takahashi, Y. Miyoshi, N. Goto, K. Honjo, "3 V operation power HBTs for digital cellular phones.", IEICE Trans. Electron., vol. E79C, pp 617-22, May 96.

3. Y. Lai, E. Chang, C. Chang, M. Tai, T. Liu, S. Wang, K. Chuang, C. Lee, "High Efficiency and Low Distortion Directly Ion-Implanted GaAs Power MESFET's for Digital Personal Handy Phone Applications", IEEE Electron Device Letters, Vol.18, No.9, pp 429-31, 1997.

4. P. Parikh, P. Chavarkar, U.K. Mishra, GaAs MESFETs on a Truly Insulating Buffer : Demonstration of the GOI Technology, IEEE EDL, vol. 18, no. 3, pp 111-14, 1997.

5. J. M. Dallesasse, N. Holonyak, Jr., A. R. Sugg, T. A. Richard, and N. El-Zein, "Hydrolyzation oxidation of  $Al_xGa_{1-x}/As$ -AlAs-GaAs quantum heterostructures and superlattices", Applied Phys.Lett., 1990 57, 2844.

6. R. Stancliff, D. Poulin, "Harmonic Load Pull", IEEE MTT-S Int. Microwave Symposium Dig., pp. 185-87, June 1979.

7. B. Hughes, A. Ferrero, & A. Cognata, "Accurate on-wafer power and harmonic measurements of mm wave amplifiers and devices", in IEEE MTT-S Int. Microwave Symp. Dig. pp. 1019-22, 1992.